# Advances in Quantum Computation and Quantum Technologies: A Design Automation Perspective

Giovanni De Micheli, *Fellow, IEEE*, Jie-Hong R. Jiang, *Member, IEEE*, Robert Rand, Kaitlin Smith, *Member, IEEE*, and Mathias Soeken, *Member, IEEE*

Abstract—Universal and fault-tolerant quantum computation is a promising new paradigm that may efficiently conquer difficult computation tasks beyond the reach of classical computation. It motivates the development of various quantum technologies. The rapid progress of quantum technologies accelerates the realization of quantum computers. In this paper, we survey the recent advances in quantum technologies and quantum computation from the design automation perspective.

${\it Index Terms-} \textbf{Design} \quad \text{automation, quantum computation,} \\ \text{quantum technology.}$

#### I. INTRODUCTION

N Moore's era during the previous half-century, the exponential growth of capacities of computing systems has sustained the semiconductor and information technology industries in transforming our daily lives. As the downscaling of transistor sizes approaches the physical limit at the atomic level, Moore's law, which predicted the number of transistors on a chip doubles every 18 to 24 months, is no longer valid. Nevertheless, the end of Moore's era and the demand for big data processing of intelligent systems gave birth to innovative design and technology solutions. For computing devices, more Moore (CMOS) and more than Moore (beyond CMOS) alternatives are under intensive research. For computing systems, new architectures (beyond the conventional von

- G. De Micheli is with EPFL, Switzerland (E-mail: giovanni.demicheli@epfl.ch).

- J.-H. R. Jiang is with National Taiwan University, Taiwan (E-mail: jhjiang@ntu.edu.tw).

- R. Rand is with the University of Chicago, USA (E-mail: rand@uchicago.edu).

- K. Smith is with the University of Chicago, USA (E-mail: kns@uchicago.edu).

GDM was supported by SNF, under grant "Supercool: Design methods and tools for superconducting electronics", 200021-1920981. JHJ was supported by the Ministry of Science and Technology of Taiwan, under Grant No. MOST 111-2119-M-002-012. RR was supported by EPiQC, an NSF Expedition in Computing, under Grant No. CCF-1730449 and the Air Force Office of Scientific Research under Grant No. FA95502110051. KNS is supported by IBM as a Postdoctoral Scholar at the University of Chicago and the Chicago Quantum Exchange; in part by EPiQC, an NSF Expedition in Computing, under award CCF-1730449; in part by STAQ under award NSF Phy-1818914; in part by NSF award 2110860; in part by the US Department of Energy Office of Advanced Scientific Computing Research, Accelerated Research for Quantum Computing Program; in part by the NSF Quantum Leap Challenge Institute for Hybrid Quantum Architectures and Networks (NSF Award 2016136); and in part based upon work supported by the U.S. Department of Energy, Office of Science, National Quantum Information Science Research Centers.

Manuscript received September XX, 20XX; revised November XX, 20XX.

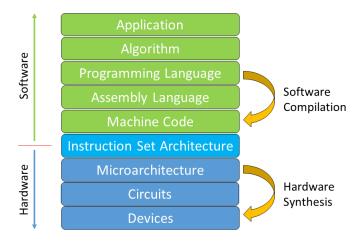

Fig. 1. Abstraction stack of classical/quantum computation.

Neumann architecture) and new computation paradigms (beyond the classical Turing machine model) are under extensive exploration.

Quantum computation (QC) is an essential new computing paradigm in post-Moore information technology. The extraordinary quantum properties, primarily superposition and entanglement, offer computation and information processing power beyond the reach of classical computers. Quantum algorithms of various sorts for computations of number factorization [1], solution search [2], quantum simulation [3], annealing [4], linear and differential equation solving [5], [6], etc., are available. They provide provable speed up over classical computation for various applications such as cryptanalysis, constraint solving, combinatorial optimization, and machine learning. Even though quantum computers are not expected to replace classical computers entirely, they are crucial technologies for certain computation accelerations. Consequently, the promise of these quantum algorithms has primarily motivated the extensive developments of quantum hardware and quantum software.

The abstraction stack of quantum computation is similar to that of classical computation as shown in Fig. 1. A more detailed and quantum-specific view on architecture is proposed in [7]. For quantum hardware, both general-purpose quantum processors, e.g., [8], and special-purpose quantum processors, e.g., [9], are under active development. The former follows the unitary-gate-based quantum circuit computation model [10], [11], and the latter follows the Ising-model-like annealing procedure [4]. Recent advancements in quantum computer

realization have demonstrated quantum advantage [8], showing the advantage of quantum computation over classical computation in a physical experiment. While building largescale fault-tolerant universal quantum computation remains a long-term challenge, quantum computers based on the noisy intermediate-scale quantum (NISQ) technology [12] are available and exploited in different applications [13], for example, notably, quantum simulations for chemical systems [14], material science [15] and drug discovery [16]. Various physical implementations of quantum processors based on superconducting quantum devices [17], [18], semiconductor quantum dots [19], trapped ions [20], photonics [21], etc., have been proposed and demonstrated. Each competing technology has its advantages and disadvantages. To fully explore the potentials of various realization means, circuits and systems need to be built based on different technologies. Also, circuits and systems interfacing quantum and classical data processing are crucial for scalable quantum computation [22], [23].

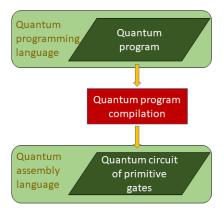

For quantum software, a full stack of software engineering is indispensable to release the full power of quantum computing. To date, quantum computation programming languages [24], operating systems [25], compilers [26]-[30], and application programs [31] are emerging. Quantum software engineering requires domain knowledge at different abstraction levels. In particular, compiling a quantum algorithm or application into a format executable on a quantum processor requires transforming a high-level programming language code into a lowlevel quantum assembly code, which consists of a sequence of unitary operations represented as quantum circuits. The compilation requires high-level, logic-gate-level, and physicallevel synthesis of design automation techniques. Also, the design of quantum algorithms and circuits has to be verified for correctness. Formal verification [32], simulation [33], and emulation [34] are vital, especially because quantum computers are intrinsically probabilistic and noisy. Many conventional electronic design automation (EDA) techniques for integrated circuit design can be applied and extended for quantum circuit compilation [35], [36].

In addition to the hardware and software aspects of quantum computing, there are important threads of developments in quantum-inspired computing systems and the hybrid quantum-classical computation. Even though fault-tolerant quantum computers are not yet ready, the concept of quantum computation itself has triggered innovative solutions that overcome conventional computation barriers. There are quantum-inspired architectures [37], [38] and algorithms [39] that improve classical computers and algorithms. Classical and quantum computations together may mutually fertilize each other and further advance our knowledge and practice of computation.

Engineering the computation systems largely requires various backgrounds in physics, computer science, electrical engineering, among others. This survey intends to summarize some key developments of design automation methods for quantum hardware and software engineering and provide helpful guides for the readers' further exploration.

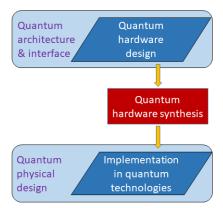

The scope of this paper covers the aspects of quantum software compilation and quantum hardware synthesis, as shown in Fig. 2. We primarily focus on general-purpose quantum computation and leave out the subject of quantum annealing. The rest of this paper is organized as follows. Section II first provides the background of quantum processor architecture. Given the instruction set architecture (ISA), i.e., primitive quantum gates, provided by a quantum processor architecture, quantum software compilation can be carried out. The literature on quantum software compilation is then surveyed in Section IV. Then Section V reviews quantum technologies and design automation methods for quantum design. Finally, Section VI concludes this survey.

#### II. QUANTUM PROCESSOR ARCHITECTURE

QCs, with their particular device physics, will require specific instruction sets, organization, and hardware to be developed into useful systems that successfully harness the power of quantum mechanics. Some examples of emerging qubit technology include discrete energy levels within superconducting circuits [8], [40], [41], ions trapped by surrounding electrodes [42]-[44], neutral atoms secured with optical tweezers [45], [46], and photons travelling through free space or waveguides [47], [48]. Each of these platforms have their unique strengths and methods for implementing logical computation, but none has become the obvious choice for the standard quantum computing platform. All of the aforementioned systems, however, must account for several similar architectural constraints in order to apply quantum superposition, interference, and entanglement for significant computational speedups in solving select problems.

No-cloning of Qubits: Although basis states, or qubits in the fixed state of either  $|0\rangle$  or  $|1\rangle$  can be duplicated, unknown qubit superposition cannot be copied. This fundamental quantum principle is referred to as the "no cloning theorem" [49], and it has serious implications on the way quantum information is to be processed and stored. In classical computation, the ability to copy bits is frequently exploited within computation, by memory, and for error correction. In quantum software and hardware, however, we loose the ability to replicate data because observing, or measuring, quantum state causes its collapse into classical information. As a result, the design of quantum memory must differ significantly from classical memory hierarchies – quantum data must be actively moved to and from stored and cannot be recovered once read. Additionally, quantum error correction relies on actively applying state transformations on unknown qubit states for stabilization rather than relying on techniques such as either refresh cycles or with copies that perform a majority vote among copies of bits like in classical schemes.

**Probabilistic Measurement:** A key feature that defines qubits from classical bits is their ability to hold superpositions of states. Upon measurement, superpositions collapse into classical states:  $|\psi\rangle = \alpha \, |0\rangle + \beta \, |1\rangle$  collapses to either 0 or 1. A single measurement of the final state transformed by a quantum circuit cannot provide adequate insight about the circuit's true output. A more complete picture of the circuit's probabilistic quantum state output must be extracted through multiple measurements that develop a distribution. From the statistics associated with this distribution, quantum

### **Quantum Software Compilation**

#### **Quantum Hardware Synthesis**

Fig. 2. Software compilation and hardware synthesis for quantum computation.

state can be inferred. Developing complete state information is possible through quantum tomography, but  $O(2^{2n})$  measurements are required for complete state estimation. This amount of measurement might be prohibitive for practical QC use. An efficient quantum program will ensure that the correct outcome has a higher likelihood of being observed through subroutines such as amplitude amplification. However, the probabilistic nature of quantum information does not completely rule out the chance of seeing an incorrect output. Other external factors, such as system noise or errors on state preparation, gate evolution, and measurement, can also result in an undesired circuit result. Thus, many runs, or shots, of a quantum algorithm may be required in order to build statistical confidence in a result. Depending on the algorithm, the number of required circuit shots can be in the thousands.

Physical Realization of Quantum Information: The principles of quantum informatics are well defined, but means to physically realize qubits and quantum operations are necessary to make the exciting theoretical promise of quantum computation a reality. According to Di Vincenzo, specific criteria are required for physical quantum architectures to host quantum computation [50]. These conditions include containing well characterized qubits that can be initialized into known states, long coherence times for holding quantum information, the ability to realize quantum gates and measurement, and the ability to interact stationary, or compute, qubits with flying qubits, or those used for communication. Currently, a variety of quantum technologies can encode logical qubits within different media. We call a physical implementation of a radix-2 unit of information a physical qubit. Since today's quantum devices lack error correction, each logical qubit within an algorithm is implemented with one physical qubit in a machine. These NISQ devices are error prone and are up to hundreds of qubits in size [12].

**Dependence on Classical Processing:** For the foreseeable future, quantum resources will be hybrid devices that will require some amount of classical co-processing. For example, in the near-term, variational algorithms [51], [52] will require classical subroutines for optimizing quantum algorithm parameters and moving closer to desired solutions. In the fault-

tolerant regime, classical programs will be required to implement the supporting mathematics required for applications such as Shor's quantum factoring [1]. In addition, classical processing will be required for quantum algorithm compilation and optimization as well as for low-level device control. Because of a QCs dependence on classical logic, quantum architecture must be designed to allow for seamless integration with classical infrastructure hosts the quantum processing unit.

Multi-qubit Interaction: To leverage entanglement within algorithms, a feature that provides many quantum algorithms with advantage, qubits must have the ability to communicate and interact. Therefore, quantum state must be able to be mobile by either physically relocating qubits or through transferring quantum state through intermediate qubits if physical qubits are in fixed locations. Additionally, in the cases where large-scale entanglement is required, complex, multi-qubit operations will need to be physically realized by operators that are native to a specific quantum machine. In NISQ computing, qubit-qubit communication is often limited to nearest-neighbors. An important consideration in near-term quantum devices and beyond will be reducing communication overheads associated with multi-qubit interactions.

Qubit Sensitivity: Classical programs running on classical hardware infrequently worry about failures in data storage or logic operations. Additionally, failures are rarely injected from the environment unless the classical device is subject to extreme conditions. A significant amount of development has allowed classical computers to be robust to errors. However, qubits are extremely sensitive to external noise and currently suffer from high error rates that corrupt computation. As an attempt to limit the amount of external environmental influence on today's QCs, many implementations require that the QC operate near absolute-zero temperatures. Despite external conditions that introduce minimal heat to the quantum system, quantum systems still suffer from detrimental as a result of imperfect control [53], device defects [54], [55], and cross talk [56]. This noise stemming from imprecision at the physical level causes operational errors that cause gates performed on qubits to diverge from their intended logic and retention errors that limit the duration of time that qubits can

4

hold state information [57].

#### III. OUANTUM PROGRAMMING LANGUAGES

Quantum programming languages can be roughly divided into two categories: Languages designed for programming the computers of today (like those operated by IBM, Google, IonQ and Rigetti computing) and those designed for future devices with error-corrected qubits that can implement sophisticated algorithms like Shor's algorithm. We will start with the first class of languages:

a) Near-term languages: The best known tool for quantum programming is almost certainly QISKIT, a set of Python libraries designed for programming IBM's quantum computers. QISKIT generates circuits written in OPENQASM, a family of Quantum Assembly Languages executable on IBM's hardware. The original QASM was designed for simply printing out quantum circuits, and its successors are similarly low-level. They describe circuits over a small set of gates, including the controlled-NOT (CNOT),  $U_1$ ,  $U_2$ , and  $U_3$ , where each of the  $U_i$  gates takes in i real numbered values.  $U_3$  can implement any single qubit rotation ( $U_1$  and  $U_2$  are redundant in principle but are included for efficiency's sake) and hence together with CNOT makes up a universal set for quantum computation. For a detailed description of these gates and their functionality we refer the reader to common introductory material, e.g., [58]. OPENQASM 2.0, the standard output for QISKIT, is quite limited in terms of describing anything beyond simple circuits. Measuring a qubit results in a bit that can then be used to control a subsequent gate, however any stronger notion of classical control flow is absent from the language.

Google's CIRQ, like QISKIT, is a Python library designed for constructing quantum circuits. CIRQ has an additional focus on timing, allowing the user to specify which gates can run in parallel and succession. In fact, CIRQ is structured around time windows called Moments, in which a certain group of operations is scheduled. Otherwise, it looks very much like QISKIT, save that there is no separate language for circuit generation and circuit execution, a common quantum programming paradigm.

The third near-term quantum programming language of note is Rigetti's PYQUIL which, like QISKIT, consists of both a low-level circuit language (the "Quantum Instruction Language" QUIL) and a Python library for constructing circuits. Like QISKIT and OPENQASM, QUIL consists of a series of quantum gates while PYQUIL exists to generate QUIL circuits, but QUIL generalizes this model slightly: QUIL provides a "Delay" function, allowing for classical computation while QUIL awaits further instruction. However, this feature, like QUIL's capacity to measure a qubit mid-compilation, isn't supported by Rigetti's machines.

Some of QUIL's forward looking features blur the gap between near-term and long-term languages. The most recent version of OPENQASM, OPENQASM 3.0 [59], does the same. Unlike prior versions of OPENQASM, this new version allows the user to describe families of circuits, parameterized by a classical input not just concrete circuits. At the same

time, drawing from CIRQ, it allows users to specify timing information on the gate level. It also allows the user to run classical computation on the results of measurements in order to compute the remainder of the circuit. Such techniques are important for quantum routines like Repeat-Until-Success or variational quantum algorithms, even though they cannot be run on IBM's current machines. In this way, OPENQASM 3.0 more closely resembles the long-term quantum programming languages that we will discuss next, even as it includes features tailored for near-term devices.

b) Long-term languages: A variety of languages have been developed for long term quantum computing. A pioneering language in this family is QUIPPER [26], a functional circuit-generation language aimed at evaluating the cost of executing advanced quantum algorithms, including a list of seven diverse and challenging algorithms proposed by IARPA. To do this, QUIPPER provides functionality for generating quantum circuit from Haskell code, bidirectional communication between classical and quantum devices, controlling and reversing of circuits, and automatic uncomputation of ancilla qubits. It can also calculate the resource costs of generated circuits, giving us a sense of the path towards long term quantum algorithms.

The SCAFFOLD language [60] was also developed to explore this path, though with a focus on optimizing circuits to make these complex algorithms more tractable [61]. SCAFFOLD is an imperative language modelled after C and aims to be an quantum algorithm description language, rather than simply a circuit generation language. It allows for the allocation of qubit registers as first class objects and for applying gates and other operations to these arrays. (Qubits, in SCAFFOLD's model, are simply qubit registers of length 1.) Like QUIPPER, SCAFFOLD provides a compiler from classical expressions to quantum ones, allowing for the easy generation of large quantum circuits that behave classically on their inputs.

Along with QISKIT, Microsoft's high-level Q# language [62] has one of the most developed libraries and active developer communities among quantum programming languages. Like SCAFFOLD, it moves away from the circuit model, instead allowing for quantum *operations* that affect the quantum state and pure classical *functions* that leave the quantum state alone. Unlike the many embedded quantum languages, Q# is self-contained and features a syntax and type system reminiscent of C# (although Q# is not a .NET language unlike C#). Q# facilitates simulation, by including certain features like an assert statement that can only be checked in simulation. To get code from Q# and other high-level language running on quantum devices, one can leverage intermediate representations such as QIR [63], which is based on LLVM.

c) Safety guarantees: There are a wide variety of ways in which quantum programs can go wrong, including trying to copy (or "clone") a qubit, sequencing quantum circuits with different numbers of wires, and discarding ancilla qubits without unentangling them and/or returning them to the  $|0\rangle$  state. Some of the earliest quantum programming languages were developed to avoid these kinds of errors, with Selinger's QPL [64] employing a syntactic check that the two arguments

to a two-qubit gate were distinct.

The most common approach to avoiding violations of the no-cloning theorem is through using *linear types*, which guarantee that linear data is used precisely once. The quantum lambda calculus [65] uses a variant of this system called *affine types*, which ensure that data is used at most once, allowing for free deletion of qubits. PROTO-QUIPPER, an idealized, self-contained core of the QUIPPER language, similarly uses linearity to prevent cloning or deletion or qubits, patching a key potential source of error in QUIPPER itself.

While linear types are used to prevent cloning, *dependent types*, in which types can depend on language-level terms, ensure that the composition of circuits is well-formed. The QWIRE language [66], embedded in the Coq proof assistant. combines both linear and dependent types to allow for the safe composition of circuits, often drawn from parameterized circuit families. In a similar vein, PROTO-QUIPPER-D [67] combines linear and dependent types, though it avoids the abstraction of separate host and circuit language. Even more recently, Chimaera [68], takes advantage of the linear and dependent types in the Idris 2 language to obtain a quantum programming language that gets no cloning and safe composition for free.

The safe management of ancilla was first addressed by REVERC, a tool for safely compiling reversible circuits, using uncomputation to discard bits. Drawing on REVERC, QWIRE was augmented with a limited range of templates for uncomputing and discarding ancilla, which were proved correct in the Coq proof assistant. The SILQ language [69] was built around safe and automatic uncomputation via qfree and const annotations that guarantee that a function behaves classically and that a given qubit isn't modified until it can be safely uncomputed. SILQ uses similar annotation to guarantee that functions can be reverse or controlled, by promising that they are measurement-free. In terms of uncomputation, the Unqomp language [70] builds upon SILQ by ensuring that uncomputation isn't merely safe but efficient.

These are merely some of the key safety guarantees made by recent quantum programming languages. Others include guaranteeing that qubits are separable from the rest of the state, as in the Twist programming language [71], through a mixture of static annotations and dynamic assertions and checks.  $\lambda_{O\#}$  [72], a proposed formal core for Q#, uses singleton types to guarantee that multiple aliases of a qubit aren't passed to the same operation, while enforcing stack discipline. PROTO-QUIPPER-DYN [73] uses type annotations to ensure that a quantum function doesn't use dynamic lifting to request a continuation from the classical computer, ensuring that the function can be safely treated not simply as a function, but as a circuit. Novel approach to safety guarantees in quantum programming language continue to appear in the literature, demonstrating how quantum computing continues to benefit from such techniques.

#### IV. QUANTUM PROGRAM COMPILERS

In this section, we survey various quantum compilation algorithms. We can think of the trace of a quantum program

as a high-level quantum circuit over n primary qubits and a sequence of high-level quantum gates that operate on a subset of these n qubits. Therefore, depending on the control flow of a program, there may exist several different quantum traces for one program, each may result in a different qubit allocation. Examples for high-level operations are the addition of two quantum registers or a quantum Fourier transform. Note that the description of high-level quantum gates may vary. Operations can be described explicitly in terms of unitary matrices or symbolically, e.g. by a Boolean function that describes a permutation or a phase change of the state's amplitudes. The goal is to execute the trace on a physical quantum computer that is characterized by number of available qubits, a target gate set of available single qubit and two qubit gate operations, and a coupling graph that describes which pairs of qubits allow the execution of two qubit gates. The synthesis step in a quantum compiler takes care of translating the high-level quantum gates to allowed operations in the target gate set, the mapping step assigns the qubits of the input trace to physical qubits and possibly changes the quantum circuit such that the constraints of the coupling map can be fulfilled.

#### A. Synthesis

1) Hierarchical synthesis: Hierarchical synthesis methods [74], [75] address the translation of high-level quantum gates that implement *Boolean oracle unitaries*

$$U_f: |x\rangle |y\rangle |0\rangle^{\otimes k} \mapsto |x\rangle |y \oplus f(x)\rangle |0\rangle^{\otimes k}, \tag{1}$$

where  $|x\rangle$  and  $|y\rangle$  are quantum registers of length m and l respectively, and  $f: \{0,1\}^m \to \{0,1\}^l$  is a Boolean function with m inputs and l outputs. When the Boolean function is represented in terms of a hierarchical logic network composed of r gates, one can readily find quantum circuits that represent  $U_f$  with  $k \leq r$  helper qubits computing temporary values onto the helper qubits using simpler quantum operations that correspond to the logic gates in the logic network. Researchers have proposed LUT (lookup table) networks [76] to limit the number of inputs to each logic gate. Various techniques to map such oracle unitaries for functions with a small number of inputs have been proposed, e.g., [77]–[79]. Other instantiations of hierarchical logic synthesis methods utilize XOR-AND-Inverter graphs (XAGs) and found that the number of helper qubits can be bounded by the number of AND gates in the XAG [80]. This enables the application of logic synthesis methods to the logic networks in order to reduce the number of AND gates. Several algorithms to reduce the so-called multiplicative complexity [81] have been proposed [82]–[84], which besides impacting synthesis in quantum program compilers, also are highly relevant in cryptography [82].

Further trade-offs between the number of quantum operations and qubits can be achieved by varying the ways in which and how often temporary operations are computed and uncomputed. These algorithms can be unified as instances of reversible pebble games [85], for which various algorithms have been proposed, both for arbitrary [86], [87] and specific graph topologies [88]–[90].

2) Phase polynomial synthesis: Another family of unitaries are phase polynomials. A phase polynomial representation [91] for a unitary  $2^n \times 2^n$  matrix U over n qubits is a tuple  $(A, (\theta_1, f_1), \ldots, (\theta_l, f_l))$ , where  $A \in GL_n(\{0, 1\})$  is a linear Boolean matrix,  $\theta_i$  are real-valued angles, and  $f_i$  are linear Boolean functions over n variables. A phase polynomial representation describes the matrix

$$U:|x\rangle\mapsto\left(\prod_{i=1}^le^{\mathrm{i}\theta_if_i(x)}\right)|Ax\rangle.$$

(2)

All quantum circuits that are composed of CNOT and  $R_1(\theta) = \operatorname{diag}(1, e^{i\theta})$  gates implement phase polynomials, and more importantly, all phase polynomials can be resented by a quantum circuit on n qubits using only CNOT and  $R_1(\theta)$  gates. Note that this quantum gate set becomes universal by including the Hadamard gate. If all rotation angles are multiples of  $\frac{\pi}{4}$ , the quantum circuits correspond to CNOT+T circuits, a subset of the Clifford+T gate set. In [91], the CNOT+T gate set was considered for re-synthesis and Tdepth optimization in Clifford+T circuits. One phase polynomial was constructed from maximal CNOT+T subcircuits and then re-synthesized in a way that minimizes T-depth based on matrioid partitioning. The work in [92] highlights the fact that there exist multiple phase polynomials for one unitary and use it for an algorithm to reduce T-count based on Reed-Muller decoders. In [93] a heuristic algorithm is presented that also reduces the number of CNOT gates in a CNOT+ $R_1$  circuit, by not increasing the number of rotation gates. A SAT-based version of the algorithm that finds the minimum number of CNOT gates is presented in [94], and variants that preserve gate coupling constraints [95]–[97]. Other correspondences between polynomials and families of quantum circuits are reported in [98] and [99].

3) Relative-phase implementations: Synthesis methods, in particular those targeting Boolean oracle unitaries, make use of multiple-controlled Toffoli gates, an X operation on a target qubit controlled on an arbitrary number of control qubits, as intermediate gate set. We can diagonalize a multiplecontrolled Toffoli gate, by surrounding the target qubit with Hadamard gates to replace the controlled X operation with a controlled Z operation. A multiple-controlled Z operation can be represented as a phase polynomial and therefore algorithms from the previous section can be applied. Smaller circuits can be found by using helper qubits and breaking down a gate with many control qubits into smaller ones with less control qubits [10]. Some initial constructions where provided in this reference, which were improved in [100] by substituting intermediate Toffoli gates by relative-phase implementations thereof, which require fewer gates from a target gate set such as Clifford+T [101]. More savings are possible when synthesizing several multiple-controlled Toffoli gates at once [102]. A dedicated construction for a three-controlled Toffoli gate is reported in [103]. Relative-gates have also been applied to reduce the cost of arithmetic operations [104], [105] or arbitrary quantum circuit optimization algorithms [106]. Some circuits make use of so-called measurement-based uncomputation [104], which can significantly reduce the cost of the quantum circuit for the cost of mid-circuit measurements. Such techniques are also useful for generalizations of the multiple-controlled Toffoli gate, e.g., table lookup [107]. The work in [108] analyzes a generalization that includes relative-phase implementations as special instances, and uses it to find improved quantum circuits.

4) Unitary synthesis: The synthesis of arbitrary unitary matrices often starts from a decomposition into CNOT gates and arbitrary single-qubit unitary matrices U [10]. Various constructive algorithms have been proposed, e.g., based on cosine-sine matrix decomposition [109], quantum multiplexors [110], decomposition of isometries [111], or meet-in-the-middle algorithms [112], [113].

Then, single-qubit gates in the resulting circuits can be described by three rotations using Euler decomposition U = $e^{i\phi}R_z(\theta_1)R_x(\theta_2)R_z(\theta_3)$ , up to a global phase  $e^{i\phi}$ . This is equal to  $e^{\mathrm{i}\phi}R_z(\theta_1)HR_z(\theta_2)HR_z(\theta_3)$ , and therefore the problem can be reduced to rotation synthesis of  $R_z(\theta)$  operations. Since the target gate set is usually finite, the rotation  $R_z(\theta)$ may not be representable using gates drawn from the target gate set. Therefore, in a first step one tries to find an approximation R for  $R_z(\theta)$  such that R can be represented using gates from the target gate set and such that  $||R - R_z(\theta)|| \le \varepsilon$ for some  $\varepsilon > 0$ . This step is called single-qubit unitary approximation [114]. First constructive algorithms were found by [115]–[117], optimal algorithms shortly after by [118]– [120] for specific gate sets and with generalizations of gate sets in [121]. Further improvements were achieved by allowing measurements in the circuits [122], [123]. The state of the art in single-qubit unitary synthesis reduces the problem to a magnitude approximation problem [124]. After an approximation was found, exact synthesis techniques [125]–[127] can be used to map them to the respective gate set.

#### B. Compilation

1) Mapping to NISQ devices: Near-term QCs have specific architectural constraints that must be considered during compilation. NISQ devices lack error correction, so each logical qubit within an algorithm is allocated to one physical qubit on a quantum processor. These physical qubits are often limited in their ability to interact directly with other qubits since as most NISQ hardware only supports nearest-neighbor coupling. As a result, the primary goal of a compiler when mapping quantum programs to near-term machines is to optimize for communication: it is preferred to determine mappings that minimize the movement of qubit state during program runtime since computation must be completed within restrictive qubit coherence windows.

Initially, linear nearest neighbor constraints on a 1D line graph or a 2D grid were considered [128]–[131]. With the emerge of coupling graphs from real devices, a method for arbitrary graphs based on A\* search was proposed [132]. Significant improvements were found by applying multiple rounds of mapping to find a good initial qubit placement [133], which was further analyzed in [134]. Other approaches are based on transformation and commutation rules [135]. SAT- and SMT-based techniques can be applied to find optimum solutions

and have first been proposed in [136] and later improved (in run-time) in [137], [138]. Other approaches suggest to apply a two-step approach in which the circuit is partitioned into maximal subcircuits for which a qubit placement can be found without changing the circuit. In a second step, SWAP networks are generated to map from one qubit placement to another between subsequent subcircuits in the partition, also called qubit routing. A SAT-based algorithm to find qubit placements for a partition was proposed in [139]. It was shown that qubit placement can be mapped to routings via matching and token swapping problems [140] depending on whether one is interested in a quantum circuit with low SWAP depth or low SWAP count, respectively. Various algorithms to solve the token swapping have been proposed in [141]. In most of these algorithms, each qubit on the target hardware was considered the same, however, the quality of individual qubits and qubit pair interactions can vary. Noise-aware mapping algorithms [142], [143] take this into account to find not only mappings with a low gate count overhead, but also those that favor qubits and qubit interactions with higher quality to reduce effects of noise. Additional examples of quantum compilation frameworks that boost the performance of algorithms on near-term machines via architecture-aware optimization include [144]–[146]

2) Mapping to surface code: Fault-tolerant quantum computing controls the noise of physical qubit operations by encoding multiple physical qubits into logical qubits through error correction. The surface code [147], [148] is a promising approach to implement such a fault-tolerant quantum computing scheme. A universal set of quantum computing operations can be implemented on top of the surface code, e.g., through lattice surgery [149]. The lower-level surface code gate set often makes use of joint-measurement operations as multiqubit operations, and applies non-Clifford gates by means of magic state distillation [150] and injection protocols [?]. Joint-measurement operations can be used to implement longrang SWAP or teleportation operations [151], which enables mapping algorithms that are favorable to SWAP-based mapping algorithms. In [152], an algorithm is proposed that transforms a quantum circuit into a sequence of high-weight Pauli measurement. In [153] proposes a mapping algorithm based on long-range operations and optimizes their scheduling by means of edge-disjoint path compilation.

#### C. Simulation

Simulation is an essential way to investigate the behavior of a quantum system. However, it is computationally challenging due to the exponential growth of quantum states in the number of quantum bits (qubits) as well as the complex domains in characterizing quantum states and operations. This difficulty motivates Richard Feynman's proposal to build a quantum simulator/computer to simulate a quantum system, rather than using a classical computer.

A quantum computation task proceeds in three steps: initial state preparation, state evolution, and measurement. In gatebased quantum computation, the state evolution is modeled by a sequence of unitary operators that update the state vector. A simulator aims to predict the measurement outcomes. Classical simulation of quantum circuits can be classified into *strong simulation* and *weak simulation*. The former aims to calculate the probabilities of the measurement outcomes with high accuracy; the latter aims to obtain output samples from the probability distribution [154]. Most simulation algorithms focus on strong simulation to calculate the probability amplitudes of one or more quantum states. In weak simulation, a classical computer mimics a quantum computer in sampling the measurement outcomes.

There are two approaches to compute probability amplitudes, namely, Schrödinger's and Feynman's approaches [8]. The former is based on state evolution by updating the state vector gate by gate. The latter is based on path integral by summing over the contributions of probability amplitudes of all paths in the configuration space.

In contrast to Schrödinger's approach computing all probability amplitudes, Feynman's can be much more memoryefficient in computing the probability amplitude of a single quantum state of interest. Tensor-network-based simulation algorithms, e.g., [155]–[157], allows the computation complexity not to grow in the number of paths, which can be exponential in the number of qubits and gates of the quantum circuit, but rather in the tree-width of the circuit graph. Essentially, the tensor *contraction* operation plays the role of path integral in summing contributing amplitudes. When the graph of a quantum circuit is closer to a tree, i.e., having a smaller value of tree-width, the circuit exhibits less quantum characteristics and can be simulated more easily by classical computers. As noted in [158], Schrödinger's approach works relatively well for quantum circuits with the number of qubits sufficiently limited for a full state vector storable in memory. In contrast, Feynman's approach works relatively well for shallow quantum circuits with a large number of qubits.

Modern quantum circuit simulators follow one of the two approaches or explore their combination. Depending on the underlying data structures, quantum circuit simulation algorithms may vary in their implementation and applicability. In the following, we review some representative implementation choices.

1) Array-based methods: One natural choice of data structures for quantum circuit simulation computation is using arrays to store the operator matrix and state vector and support their multiplication in Schrödinger's approach and to store tensors and support their contraction in Feynman's approach.

Simulation by array-based matrix-vector multiplication is commonly available in quantum compilation and simulation tools, e.g., CIRQ [159], QISKIT [160], QUEST [161], QULACS [158]. Although matrix-vector multiplication is well supported by parallel computations on CPUs and GPUs, the full-amplitude computation is hardly scalable to circuits with 50 qbuits even with supercomputing facilities. On the other hand, simulation by array-based tensor-network contraction has been developed and available in tools, e.g., QUIMB [162], QULACS [158]. As the method allows partial and single amplitude computation, it may reduce the memory requirement and allow simulation on larger circuits. As was demonstrated in [163], random quantum circuits with 40, 75 and 200 qubits

can be simulated for the computation of full, partial and single amplitude, respectively.

2) Decision-diagram-based methods: Binary decision diagrams (BDDs), particularly the reduced ordered BDDs (ROB-DDs) [164], have been widely used as a compact canonical representation for Boolean function manipulation. Efficient BDD packages, e.g., [165], are available and widely applied in various applications, such as electronic design automation and formal verification. The success has motivated their extension, e.g., [166]–[169], to quantum circuit simulation to overcome the memory explosion problem of array-based methods. The quantum multiple-valued decision diagram (QMDD) [170] is one of such attempts to represent and manipulate operator matrices and state vectors of complex values. The QMDDbased simulation [168] is shown more effective than the arraybased simulation in [171] in cases where quantum states can be compactly represented by QMDDs. QMDDs have been applied to confirm that program semantics are preserved during compilation [172].

Most array-based and QMDD-based methods rely on floating-point numbers to represent complex values and may suffer from the precision problem [173]. The problem is overcome in [169], [173], where a complex number is represented algebraically using five integer coefficients. In [173], the floating-point numbers in a QMDD are replaced with algebraic complex numbers at the cost of computation overhead due to more expensive arithmetic operations. In contrast, in [169] the algebraic integer coefficients are represented with an ROBDD per bit of an integer coefficient. Simulating an n-qubit quantum circuit corresponds to manipulating n-variable ROBDDs according to a set of pre-characterized Boolean formulas corresponding to the multiplication effects of the supported set of unitary operators. It simulates certain benchmarks up to tens of thousands qubits, and is generally much more scalable than QMDD-based methods. Although [169] supports only algebraically representable unitary gates, the gate collection is already sufficient for universal quantum computation.

The above decision-diagram-based methods follow Schrödinger's approach for quantum state evolution. Nevertheless, decision diagrams can also be applied in Feynman's approach for tensor-network-based computation [174], where a QMDD is relaxed to allow the input and output variables of a qubit to be freely, rather than adjacently, ordered and the tensor contraction operation on decision diagrams is supported.

3) Stabilizer-rank methods: There are classes of quantum circuits whose simulation on a classical computer takes time polynomial in the circuit size. One well-known class is the stabilizer circuits, which merely consist of Clifford gates. Any Clifford gate can be generated using the CNOT, Hadamard, and phase gates. Algorithms for efficient simulation of stabilizer circuits has been proposed [175], [176].

As universal quantum computation can be achieved by Clifford gates added with some non-Clifford primitive gates, e.g., the T-gate, or with the magic state, the stabilizer circuit simulation algorithm can be extended to detail with circuits with both Clifford and non-Clifford gates [175]. Unsurprisingly, the time complexity grows polynomial in the number of Clifford gates

and exponential in the number of non-Clifford gates. There are recent efforts [177]–[179] that attempt to alleviate the exponential growth through the notion of *stabilizer rank* [178] by decomposing a state into the superposition of a number of stabilizer states [177].

#### D. Verification

1) Equivalence checking: In modern integrated circuit (IC) design flow, equivalence checking plays an important role in ensuring the synthesis steps do not introduce errors. Similar verification requirements are needed in the compilation of quantum programs because the process of quantum program compilation corresponds to a sequence of quantum circuit transformation. In the compilation process, the circuits before and after synthesis have to conform to some equivalence criteria. The strongest and most common notion of equivalence is total equivalence, which requires the output quantum states of the two quantum circuits under verification have to be the same modulo a global phase difference.

It is clear that a quantum circuit simulator capable of strong simulation and computing all amplitudes can be used for checking total equivalence. Decision-diagram-based simulation algorithms are advantageous in equivalence checking over array-based counterparts in their canonicity in state vector representation. This canonicity makes equivalence checking easy without having to check individual equivalences of corresponding amplitude pairs, which can be exponential in the number of qubits.

Equivalence checking of quantum circuits have been studied extensively, e.g., [180]-[183]. A commonly adopted approach to checking the equivalence between two circuits  $U = U_n \cdots U_1$  and  $V = V_m \cdots V_1$ , for unitary operators  $U_i$  and  $V_j$ , is to build the *miter circuit* [181], namely,  $M=U\cdot V^{-1}=(U_n\cdots U_1)\cdot (V_1^{-1}\cdots V_m^{-1}).$  The two circuits are equivalence if and only if  $M=e^{i\theta}I$ , that is, M equals an identify operator up to some global phase  $e^{i\theta}$ . The equivalence checking boils down to computing the multiplication  $(U_n \cdots U_1) \cdot (V_1^{-1} \cdots V_m^{-1})$ . In fact, the sequence of multiplying out the matrices is flexible and can be exploited to keep decision diagrams of small size. In [182], the multiplication sequence is rewritten as  $U_n \cdots U_1 \cdot I \cdot V_1^1 \cdots V_m^{\dagger}$ . The procedure of [182] starts from the identity matrix I in the middle of the sequence and gradually multiplies either to the left or to the right under some strategies to keep the QMDD compact throughout the multiplication process. However, the above matrix multiplication suffers from the floating-point precision problem, which may lead to incorrect answers to equivalence checking. The precision problem of equivalence checking is overcome in [183], which extends the ROBDDbased algebraic representation of state vectors [169] to unitary operators. Besides equivalence checking, fidelity checking and sparsity checking are considered in [183]. Essentially, fidelity checking offers a quantitative way to tell how similar two circuits are if they are not equivalent. The ROBDD-based method [183] can check certain circuits up to thousands of qubits, and is generally more scalable and robust than QMDDbased method [182].

In contrast to the above equivalence checking methods, which follow the Schrödinger's approach, a path-sum formulation following Feynman's approaches is proposed in [32] for quantum circuit verification, including equivalence checking. However, its scalability can be limited to circuits up to 100 qubits.

There are recent efforts that extend the notion of equivalence. Specifically, equivalence checking of noisy quantum circuits is addressed in [183], [184]. In [185], partial equivalence checking is defined and realized under the ROBDD-based framework [183] to allow observational equivalence with respect to partial measurement and constrained initial states. In [186], equivalence checking of sequential quantum circuits is formulated. For dynamic quantum circuits, where quantum systems interact classical controls, their equivalence checking is considered in [187], [188].

2) Proof assistants: Formal verification of quantum programs aims to prove that a program does what it's expected to do. Two of the earliest works in this area used the Coq proof assistant [189] to prove the correctness of basic quantum algorithms, whether expressed directly as a series of quantum operations [190] or within the QWIRE quantum programming language [191]. However, the first approach was limited by a slow underlying matrix library, while the second was limited by the complexity of the QWIRE language [66], and neither was able to verify complex algorithms like Shor's factoring algorithm or Grover's search.

One approach to the complexity of verifying quantum computation was to represent them as *path-sums* [32], which describe a unitary circuits action on basis states as

$$|x\rangle \to \frac{1}{\sqrt{2^m}} \sum_{y=0}^{2^m - 1} e^{2\pi i P(x,y)/2^m} |f(x,y)\rangle$$

where P and f are drawn from a restricted class of functions. Conveniently, most common quantum gates can be represented using path-sums: For instance, the common X and T gates can be written

$$X: |x\rangle \to e^0 |x \oplus 1\rangle$$

$T: |x\rangle \to e^{2\pi i \frac{x}{8}} |x\rangle$

Path-sums can also be composed neatly, allowing for easy processing of a quantum program. Using path-sums, the FEYNMAN tool [32] was able to verify the correctness of a quantum Fourier transform on up to 31 qubits and a hiddenshift algorithm on up to 60, both in a matter of seconds. However, as we might expect, this method scales poorly, typically stalling out in the hundreds of qubits (depending on the algorithm).

In order to reason about quantum programs over arbitrary numbers of qubits (circuit families if we're considering the quantum circuit model), we have to do symbolic reasoning, where the number of qubits n appears in the verification statement and proof. QBRICKS [192] does this by generalizing FEYNMAN's path-sums to parameterized path-sums, where parameters to the program can also appear in the proof statement. Using this generalization of path-sums and the verification tool WHY3 [193], along with a range of SMT solvers, QBRICKS was able to verify a range of quantum programs, importantly

including both Grover's and (the quantum part of) Shor's algorithms, regardless of input size.

Concurrently with QBRICKS, a different group of researchers developed SQIR [194], a small quantum intermediate representation designed for ease of proof. SQIR provides it's programs semantics both in terms of unitary matrices and superoperators, for programs including measurement. While less automated than QBRICKS, it does provide some automation for simplifying matrix and complex number expressions, and switching between representations of states and operators. SQIR was originally used to prove the quantum parts of Grover's and Shor's algorithms, with later work presenting an end-to-end proof of Shor's algorithm, including the classical parts [195]. It also served as the core of the VOQC compiler [30], which heavily optimizes quantum programs while guaranteeing that the output program is semantically identical to the input.

3) Program logics: Another, partially overlapping, approach to validating quantum programs is using a program logic in the model of Hoare logic or guarded command language. The first work in this direction was D'Hondt and Panangaden's Quantum Weakest Preconditions [196], which proposed that quantum observables are the correct quantum analogue to Kozen's arithmetic predicates [197] for reasoning about probabilistic programs. Ying [198] used these predicates to write a Hoare-style logic for reasoning about programs in a quantum while language, a simple simple imperative language with quantum bits and integers, unitary application, and if and while statement, each of which measure quantum states. Ying's paper included logics for both partial and total correctness, where the former treats non-terminating programs as satisfying the postcondition. In the case of total correctness, the logic includes a rule for while loops that guarantees that the loop terminates with probability 1. The logic, later called QHL, was sufficient to prove the correctness of Grover's algorithm.

A variety of works built on QHL, including extending it to reason about both quantum and classical variables. At the same time, several works moved away from using observables as preconditions, arguing that it's often easier to reason using projectors as predicates over quantum states. These predicates were adopted in an applied quantum Hoare logic [199], which added rules for reasoning about programs with error bounds, as we expect for all near-term quantum programs. This logic was used to prove the correctness of the Harrow-Hassidim-Lloyd algorithm [5]. Simultaneously, Unruh [200] developed a projection-based quantum Hoare logic with ghost variables, where non-program variables called ghosts can stand in for measured variables in predicates. This allows one to easily express notions like "q is the outcome of a coin flip" by saying "q can be modelled as a member of a measured Bell pair with the ghost q". This logic is used for cryptographic purposes, particularly to verify a quantum one-time pad.

Quantum Hoare logic has been extended to a variety of additional domains including reasoning about program robustness [201], parallel programming [202], separation logic [203], [204], and an EasyCrypt-style relational logic for proving security [205]. The last is of particular interest as it led to qrhl-tool, a dedicated cryptographic proof assistant built

upon Isabelle/HOL [206]. QHL itself was also embedded in Isabelle/HOL [207], providing the correctness guarantees of a proof assistant along with the convenience of a Hoare style logic.

A fuller discussion of formal verification in the quantum setting is given in [208].

#### V. QUANTUM TECHNOLOGY IN COMPUTING SYSTEMS

In this section, we provide an overview how superconducting quantum technology is applied in computing systems that process either quantum or classical information.

#### A. Superconducting devices for quantum computing

Pinpointing the technology that will enable large-scale quantum computation is currently an active area of research. In the last decade, however, superconducting (SC) quantum circuits [209] have amassed popularity from industry and academia alike as a means for creating physical qubits. A leading advantage of SC circuits is that they take advantage of well-established classical fabrication techniques and thus are poised to be favorable for scaling.

SC qubits utilize Josephson Junctions (JJs), or two superconducting electrodes separated by a thin, insulating tunnel barrier, along with additional capacitors and inductors to implement circuit quantum electrodynamics (cQED). At a highlevel, cQED describes how microwave photons and SC circuits interact, and it can be used to define the rules for the realization of quantum information. SC circuits are highly configurable. For example, the properties, dimensions, and number of JJs within an SC circuit influences how the resulting qubit stores and manipulates quantum state. SC cQED devices operate at close to absolute zero temperatures, 20 mK, in order to isolate operational modes from external environmental noise - they act as mesoscopic-scale, artificial atoms with an anharmonic energy spectrum [210], [211]. Typically, the lowest two energy levels of this spectrum are used to realize qubit states: the ground state  $|0\rangle$  corresponds to the lowest energy level and the excited state  $|1\rangle$  corresponds to the next highest energy

In this section, we will focus our study on the SC qubit referred to as the transmon. We note, however, that other types of SC quantum devices based on the JJ exist such as the fluxonium [212] and flux qubit [213]. Transmons were originally developed in 2007 [214] and are the qubits found in the majority of today's cQED devices. The first two-qubit interaction of fidelity higher than 99% was demonstrated in 2014 [215], and there have been many more qubit-qubit couplings of similar quality reported since [41], [216]–[218]. Single-qubit operations can be implemented at higher fidelity with error rates of order  $10^{-4}$ . Broadly, transmon qubits are categorized as 'fixed-frequency' with a single JJ or 'fluxtunable' with two parallel JJs that allow qubit frequency to be adjusted with the application of an external magnetic field. The frequency of a transmon qubit corresponds to the difference between the  $|1\rangle$  and  $|0\rangle$  energy levels in the transmon's anharmonic spectrum.

Emerging transmons QCs are promising but are still NISQera prototypes with under 150 qubits [219]–[221]. They also suffer from non-trivial noise during computation stemming from limited coherence windows (currently in the range of 10s of microseconds) [222], measurement errors [223], and imprecise control that results from incomplete system characterization [224]. Since transmon devices are not error corrected, quantum programs must be transformed into highly-customized executables to both optimize for native gate sets and mitigate platform-specific noise on near-term QCs [142]. Although much progress has been made in terms of boosting two-qubit gate fidelity, one of the of the biggest challenges facing today's transmon qubits is obtaining qubitqubit interaction fidelities that satisfy thresholds required for fault tolerance. Flux-tunable quantum devices enable twoqubit interactions via dynamically tuning qubits into resonance conditions [225], [226] or via parametric modulation of tunable elements [227], [228]. Tunability of SC qubit circuits, however, comes at the cost of qubit coherence and implementation scalibility due to the footprint of the necessary classical control hardware. Conversely, two-qubit interactions are enabled by carefully designed microwave drives in fixedfrequency SC qubit devices [216]. The qubit frequencies of nearest and next-nearest neighbors must be allocated with adequate spacing to avoid frequency collisions and poor qubit interactions in fixed frequency devices [229]. Unfortunately, imprecision associated with today's QC fabrication causes small imperfections to appear in JJ positioning, component dimensions, and surrounding layers, influencing operational characteristics of transmons during computation [230]. In the case of the fixed-frequency transmons, fabrication imprecision that results in component imperfections often causes qubit frequency to deviate from its ideal, resulting in spectral overlaps that induce frequency collisions. Despite challenges associated with frequency collisions, however, fixed-frequency transmons are characterized by recent improvements in coherence, stability, and controlability [231]–[234] that making them promising for scaling.

## B. Superconducting electronics in classical pipelined computing

Quantum computing leverages two important properties at the device level: superposition and entanglement. Other technologies and architectures can exploit device quantum properties different that superposition and entanglement, and thus realize classical (as compared to quantum) computing with specific important characteristics. Indeed, *superconducting electronic* (SCE) circuits provides us with the ability of realizing digital logic gates where the information is quantized. Logic gates can be designed so that a single quantum of information is exchanged. Moreover, information transmission is very rapid on wires, because of the lack of parasitic resistance in the superconducting domain, typically at few degrees Kelvin (typically 4 K). Switching is achieved by *Josephson junctions* (JJ), that are designed by interposing a thin insulator in a gap of a superconducting wire of Niobium.

Superconducting electronics are quite attractive for the following reasons. First, the technology can match and extend

present performance requirements, e.g., ALU prototypes have been shown to run at and above 50 GHz clock rates. Second, SCE devices manipulate flux quanta  $\emptyset = h/2e$  with energy  $2 \cdot 10^{-19} J$  or  $5 \cdot 10^3 \ kT \ ln \ 2$  at 4 K. Thus, SCE circuits can be realized to operate much closer to the minimum energy limit, and roughly two orders of magnitude better as compared to CMOS. This prediction is confirmed by prototypes [235]. Third, these circuits can work as interface at 4 K between the host and a quantum computer, enabling information processing in a classic way that is in local proximity to a quantum chip. Thus, superconducting electronic circuits can be employed as both standalone accelerators and as bridges to quantum computing. For this last reason, an expanded description is justified here.

IBM led a strong effort in SCE in the 70s with the objective of building computers that would outperform the currently-available technology. The circuits utilized Josephson junctions exhibiting hysteresis in their resistive states (i.e., resistive and superconductive). The JJ acts as a switch that can be set and reset by applying a current. A logic TRUE is associated with the JJ in its resistive state, and a logic FALSE with its superconductive state. This effort faded in the mid 80s, because of various drawbacks, including the choice of materials and the latching operation of logic [236].

Likharev [236] brought back strong interest in SCE by proposing rapid single flux quantum (RSFQ) circuits. In these circuits, the logic values (TRUE, FALSE) are represented by the presence or absence of single flux quantum (SFQ) pulses called fluxons with  $\phi = h/2e = 2 \cdot 10^{-15}Wb$ corresponding approximately to a 2 mv pulse lasting 1 ps. Junctions are DC biased and when a pulse is applied to the junction, it can be sufficient to drive the current level over its threshold and to generate another pulse that can be propagated through the circuit. This type of behavior is often called Josephson transmission line (JTL) and it is the basic operational principle of RSFQ circuits that propagates flux pulses. A specific feature of RSFQ circuits is that logic gates are clocked, and that the overall circuit is pipelined. The RSFQ technology evolved in many directions. Energy-efficient SFQ (eSFQ and ERFSQ) [237] and low-voltage RSFQ (LV-RSFQ) [238] employ specific bias networks and low supply voltages respectively to reduce the power consumption. Dynamic flux single quantum (DSFQ) logic [239] introduces selfresetting gates that ease the clocking requirements. Various realizations of ALUs have been reported, with deep-pipelined, wave-pipelined and asynchronous operation.

SCE circuit design has several peculiarities and constraints, that may vary in the different SCE families. We highlight two constraints. First, each gate is triggered by a clock or bias signal in conjunction with the logic input signal. Thus, circuits operate in pipelined mode, and input to logic gates have to be present simultaneously, thus requiring that logic inputs have the same logic depth or distance from the primary inputs. A circuit with such a property is said to be balanced. Second, logic gates generate pulses that cannot sustain multiple fanouts, and thus splitters have to be used. As a result, SCE design requires specific electronic design tools. The Coldflux project [240], under the auspices of the IARPA Supertools

program, has addressed design electronic design automation (EDA) problems for SCE, including automatic circuit balancing [241], [242] and splitter insertion [243]. Some researchers addressed the splitter and buffer insertion in AQFP [244]-[246] while others considered a flow where the logic network is reduced first for depth using algebraic methods, followed by Boolean substitution and splitter insertion [247]. Lee presented an exact formulation of buffer/splitter insertion via SMT as well as an improved heuristic algorithm [248]. Researchers at Synopsys recently published the results of a full synthesis of a 4-bit AMD 2901 microcontroller from RTL code to layout in an ERFSQ standard cell library from Hypres [249]. Several research activities have addressed physical design of SCE circuits, such as synchronization [250], placement and routing [250]–[252], cell libraries [252], and parasitics extraction and mitigation [253]. Krylov and Friedman [254] have recently authored a comprehensive book on various aspect of SCE design with a wide set of references to current works.

#### C. Adiabatic superconducting electronics

Recent research work has addressed technologies that target low-energy consumption. This can be achieved by using adiabatic mode of operation and AC power (i.e., alternating current supply). Two technologies are particularly relevant: reciprocal quantum logic (RQL) [235] researched and developed at Northrop Grumman, and adiabatic quantum flux parametron (AQFP) [255] pursued at Yokohama National University (YNU) in Japan. A parametron is a resonant circuit with a nonlinear reactive element [256]. We describe AQFP in more detail.

The fundamental element in AQFP is the clocked buffer. Two loops, involving each a JJ and an inductor, are used to store logic information in terms of flux quanta depending on the direction of an input current signal and the magnetic coupling to other inductors. When an input and the supply trigger are present, an output current pulse is generated. The direction of the current pulse encodes the logic value TRUE or FALSE. A buffer can be made into an inverting buffer by switching the terminals of the output coupled inductor. Thus, inversion comes at no cost in this technology. It was shown [257], [258] that the "parallel combination" of three AQFP buffers yields a majority gate, which is the basic logic primitive of this technology. The 2-input logic AND and OR gates can be realized by modifying one buffer (of the majority gate) so that a small imbalance in the loop design yields always a logic FALSE or TRUE as output respectively. Based on these principles, a simple and modular cell library can be built from buffers (regular, inverted or modified) and branch cells (used to join and split signals) [257]. A full EDA flow from an HDL description to a cell-based physical design has been created by researchers at YNU [259]. In particular, tools for logic synthesis need to address balancing, majority-based synthesis (described in the next section) and splitter insertion [245]— [247].

The majority paradigm in logic synthesis [260], [261] is based on a formulation of a new Boolean algebra using the majority and complementation operators. The algebra

can be expressed in terms of five axioms (commutativity, associativity, distributivity, majority and self-duality) and was shown to be sound and complete [261]. From a theoretical standpoint, algorithms based on the majority paradigm enable the search for an optimum or optimal solution in a connected design space, which provides the existence of a path to the optimum (even though such path may be hard to find and with over-polynomial length, as the problem is computationally intractable). From a practical standpoint, tools based on the majority algebra were shown to achieve circuits 15% better in delay in average as compared to other methods after physical design in ASICs [261]. This fact was also validated on commercial tools. Libraries of algorithms for logic optimization are publicly available, such as the mockturtle library (https://github.com/lsils/mockturtle).

#### D. Wave pipelining

Wave pipelining (WP) [262] is a technique to speed up the computation by allowing two or more waves of signals to propagate in between two registers. In a WP circuit the clock frequency of the registers can be higher than the maximum propagation delay, to capture wave-fronts of data as they propagate from the source to the sink register. It is quintessential that the waves do not mix, which implies that I/O paths need to have the same delay, or to mismatch by a small quantity that eventually poses a bound on the clock frequency. There are examples of RSFQ ALU designs that exploit wave pipelining [263]. Whereas in standard (synchronous) RSFQ the clock triggers the computation at logic gates, in asynchronous wave-pipelined RSFQ signals are held so that a logic stage does not start operating until all signals from the previous stage are available. This obviates the local clocking [264] and enables multiple data waves to propagate simultaneously. As the overall performance is limited by the signal arrival-time mismatches, then SCE can benefit from path delay equalization as in CMOS WP [262] and furthermore WP path balancing can be combined with majority logic synthesis transformations, to achieve correct and optimal SCE digital circuits.

#### E. Summary

Recent realizations of SCE circuits have shown remarkable performances. For example, Ke [265] showed the realization of a low-power 8-point, 7-bit FFT processor running at 47.8 GHz consuming 5.3mW in SFQ technology. An AQFP adiabatic processor has been realized [244] with switching energy at 1.4 zJ with a 5 GHz AC clock. Even by considering a 1000x energy loss in cryocooling, this realization is still two-orders of magnitude more efficient as compared to 7nm CMOS according to [244]. These very positive results make us very optimistic about the potentials of SCE as a superconducting technology, especially for low-energy high-throughput computation. Nevertheless, scaling up SCE design is challenging, as the support of EDA tools is still in its infancy.

#### VI. CONCLUSIONS

In this survey paper, we covered recent advances in quantum computation and quantum technologies from the design automation perspective. Due to the rapid progress and diversified interdisciplinary studies, it is not possible to mention all important related work of the intended subject. However, we tried to provide a skeleton of some key elements in the abstraction stack of quantum computation sketched in Fig. 1 based on our limited knowledge. We hope this survey can serve as a helpful guide for the readers to find entry points for further investigations.

#### REFERENCES

- [1] P. W. Shor, "Polynomial-time algorithms for prime factorization and discrete logarithms on a quantum computer," *SIAM Journal on Computing*, vol. 26, no. 5, pp. 1484–1509, 1997. [Online]. Available: https://doi.org/10.1137/S0097539795293172

- [2] L. K. Grover, "A fast quantum mechanical algorithm for database search," in *Symposium on Theory and Computing*, 1996, pp. 212–219. [Online]. Available: http://doi.acm.org/10.1145/237814.237866

- [3] S. Lloyd, "Universal quantum simulators," *Science*, vol. 273, no. 5278, pp. 1073–1078, 1996. [Online]. Available: https://www.science.org/doi/abs/10.1126/science.273.5278.1073

- [4] T. Kadowaki and H. Nishimori, "Quantum annealing in the transverse Ising model," *Physical Review E*, vol. 58, no. 5, pp. 5355–5363, nov 1998. [Online]. Available: https://doi.org/10.1103%2Fphysreve. 58.5355

- [5] A. W. Harrow, A. Hassidim, and S. Lloyd, "Quantum algorithm for linear systems of equations," *Physical review letters*, vol. 103, no. 15, p. 150502, 2009.

- [6] D. W. Berry, "High-order quantum algorithm for solving linear differential equations," *Journal of Physics A: Mathematical and Theoretical*, vol. 47, no. 10, p. 105301, feb 2014. [Online]. Available: https://doi.org/10.1088\%2F1751-8113\%2F47\%2F10\%2F105301

- [7] N. C. Jones, R. V. Meter, A. G. Fowler, P. L. McMahon, J. Kim, T. D. Ladd, and Y. Yamamoto, "Layered architecture for quantum computing," *Physical Review X*, vol. 2, no. 3, jul 2012. [Online]. Available: https://doi.org/10.1103\%2Fphysrevx.2.031007

- [8] F. Arute, K. Arya, R. Babbush, D. Bacon, J. Bardin, R. Barends, R. Biswas, S. Boixo, F. Brandao, D. Buell, B. Burkett, Y. Chen, J. Chen, B. Chiaro, R. Collins, W. Courtney, A. Dunsworth, E. Farhi, B. Foxen, A. Fowler, C. M. Gidney, M. Giustina, R. Graff, K. Guerin, S. Habegger, M. Harrigan, M. Hartmann, A. Ho, M. R. Hoffmann, T. Huang, T. Humble, S. Isakov, E. Jeffrey, Z. Jiang, D. Kafri, K. Kechedzhi, J. Kelly, P. Klimov, S. Knysh, A. Korotkov, F. Kostritsa, D. Landhuis, M. Lindmark, E. Lucero, D. Lyakh, S. Mandrà, J. R. McClean, M. McEwen, A. Megrant, X. Mi, K. Michielsen, M. Mohseni, J. Mutus, O. Naaman, M. Neeley, C. Neill, M. Y. Niu, E. Ostby, A. Petukhov, J. Platt, C. Quintana, E. G. Rieffel, P. Roushan, N. Rubin, D. Sank, K. J. Satzinger, V. Smelyanskiy, K. J. Sung, M. Trevithick, A. Vainsencher, B. Villalonga, T. White, Z. J. Yao, P. Yeh, A. Zalcman, H. Neven, and J. Martinis, "Quantum supremacy using a programmable superconducting processor," Nature, vol. 574, pp. 505–510, 2019.

- [9] M. W. Johnson, M. H. S. Amin, S. Gildert, T. Lanting, F. Hamze, N. Dickson, R. Harris, A. J. Berkley, J. Johansson, P. Bunyk, E. M. Chapple, C. Enderud, J. P. Hilton, K. Karimi, E. Ladizinsky, N. Ladizinsky, T. Oh, I. Perminov, C. Rich, M. C. Thom, E. Tolkachea, C. J. S. Truncik, S. Uchaikin, J. Wang, B. Wilson, and G. Rose, "Quantum annealing with manufactured spins," *Nat.*, vol. 473, no. 7346, p. 127, 2011. [Online]. Available: https://doi.org/10.1038/nature10012

- [10] A. Barenco, C. H. Bennett, R. Cleve, D. P. DiVincenzo, N. Margolus, P. Shor, T. Sleator, J. A. Smolin, and H. Weinfurter, "Elementary gates for quantum computation," *Physical Review A*, vol. 52, no. 5, p. 3457, 1995.

- [11] E. T. Campbell, B. M. Terhal, and C. Vuillot, "Roads towards fault-tolerant universal quantum computation," *Nature*, vol. 549, no. 7671, pp. 172–179, sep 2017. [Online]. Available: https://doi.org/10.1038\%2Fnature23460

- [12] J. Preskill, "Quantum computing in the NISQ era and beyond," *Quantum*, vol. 2, p. 79, 2018, arXiv preprint arXiv:1801.00862v3.

- [13] A. D. Corcoles, A. Kandala, A. Javadi-Abhari, D. T. McClure, A. W. Cross, K. Temme, P. D. Nation, M. Steffen, and J. M. Gambetta, "Challenges and opportunities of near-term quantum computing systems," *Proceedings of the IEEE*, vol. 108, no. 8, pp. 1338–1352, aug 2020. [Online]. Available: https://doi.org/10.1109\%2Fjproc.2019. 2954005

- [14] A. Kandala, A. Mezzacapo, K. Temme, M. Takita, M. Brink, J. M. Chow, and J. M. Gambetta, "Hardware-efficient variational quantum eigensolver for small molecules and quantum magnets," *Nature*, vol. 549, pp. 242–246, 2017, arXiv preprint arXiv:1704.05018.

- [15] H. Ma, M. Govoni, and G. Galli, "Quantum simulations of materials on near-term quantum computers," npj Computational Materials, vol. 6, no. 1, jul 2020. [Online]. Available: https://doi.org/10.1038\%2Fs41524-020-00353-z

- [16] Y. Cao, J. Romero, and A. Aspuru-Guzik, "Potential of quantum computing for drug discovery," *IBM Journal of Research and Development*, vol. 62, no. 6, pp. 6:1–6:20, 2018.

- [17] P. Krantz, M. Kjaergaard, F. Yan, T. P. Orlando, S. Gustavsson, and W. D. Oliver, "A quantum engineer's guide to superconducting qubits," *Applied Physics Reviews*, vol. 6, no. 2, p. 021318, jun 2019. [Online]. Available: https://doi.org/10.1063\%2F1.5089550

- [18] M. Kjaergaard, M. E. Schwartz, J. Braumüller, P. Krantz, J. I.-J. Wang, S. Gustavsson, and W. D. Oliver, "Superconducting qubits: Current state of play," *Annual Review of Condensed Matter Physics*, vol. 11, no. 1, pp. 369–395, mar 2020. [Online]. Available: https://doi.org/10.1146\%2Fannurev-conmatphys-031119-050605

- [19] L. M. K. Vandersypen and M. A. Eriksson, "Quantum computing with semiconductor spins," *Physics Today*, vol. 72, no. 8, pp. 38–45, 2019. [Online]. Available: https://doi.org/10.1063/PT.3.4270

- [20] I. Pogorelov, T. Feldker, C. D. Marciniak, L. Postler, G. Jacob, O. Krieglsteiner, V. Podlesnic, M. Meth, V. Negnevitsky, M. Stadler, B. Höfer, C. Wächter, K. Lakhmanskiy, R. Blatt, P. Schindler, and T. Monz, "Compact ion-trap quantum computing demonstrator," *PRX Quantum*, vol. 2, no. 2, jun 2021. [Online]. Available: https://doi.org/10.1103\%2Fprxquantum.2.020343

- [21] M. Gong, S. Wang, C. Zha, M.-C. Chen, H.-L. Huang, Y. Wu, Q. Zhu, Y. Zhao, S. Li, S. Guo, H. Qian, Y. Ye, F. Chen, C. Ying, J. Yu, D. Fan, D. Wu, H. Su, H. Deng, H. Rong, K. Zhang, S. Cao, J. Lin, Y. Xu, L. Sun, C. Guo, N. Li, F. Liang, V. M. Bastidas, K. Nemoto, W. J. Munro, Y.-H. Huo, C.-Y. Lu, C.-Z. Peng, X. Zhu, and J.-W. Pan, "Quantum walks on a programmable two-dimensional 62-qubit superconducting processor," *Science*, vol. 372, no. 6545, pp. 948–952, may 2021. [Online]. Available: https://doi.org/10.1126\%2Fscience.abg7812

- [22] J. C. Bardin, E. Jeffrey, E. Lucero, T. Huang, S. Das, D. T. Sank, O. Naaman, A. E. Megrant, R. Barends, T. White, M. Giustina, K. J. Satzinger, K. Arya, P. Roushan, B. Chiaro, J. Kelly, Z. Chen, B. Burkett, Y. Chen, A. Dunsworth, A. Fowler, B. Foxen, C. Gidney, R. Graff, P. Klimov, J. Mutus, M. J. McEwen, M. Neeley, C. J. Neill, C. Quintana, A. Vainsencher, H. Neven, and J. Martinis, "Design and characterization of a 28-nm bulk-CMOS cryogenic quantum controller dissipating less than 2 mw at 3 k," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 11, pp. 3043–3060, 2019.